# Programmer's Reference Manual for AALI Interface

Part # (MANU0023-02)

(May, 1997)

# FORE Systems, Inc.

1000 FORE Drive

Warrendale, PA 15086-7502

Phone: 412-742-4444

FAX: 412-742-7742

# **Legal Notices**

Copyright  $^{\odot}$  1997 by FORE Systems, Inc. - Printed in the USA.

All rights reserved. No part of this work covered by copyright may be reproduced in any form. Reproduction, adaptation, or translation without prior written permission is prohibited, except as allowed under the copyright laws. The information in this document is subject to change without notice.

RESTRICTED RIGHTS LEGEND. Use, duplication, or disclosure by the government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 (October 1988) and FAR 52.227-19 (June 1987).

### **TRADEMARKS**

FORE Systems<sup>®</sup> is registered trademarks of FORE Systems, Inc.

ForeRunner is a trademark of FORE Systems, Inc.

Intel and i960 are registered trademarks of Intel Corporation.

SunOS is a trademark of Sun Microsystems, Inc.

SPARC is a registered trademark of SPARC International, Inc. Products bearing the SPARC trademark are based on an architecture developed by Sun Microsystems, Inc.

UNIX is a registered trademark of UNIX Systems Laboratories, Inc., in the U.S.A. and other countries.

All other brand or product names are trademarks or registered trademarks of their respective companies or organizations.

| Preface    |                                                     |             |

|------------|-----------------------------------------------------|-------------|

| Typogr     | cal Supportaphical Stylesant Information Indicators | i           |

| CHAPTER 1  | Introduction                                        |             |

| 1.1        | Introduction                                        | . 1-1       |

|            | 1.1.1 Overview                                      |             |

| 1.2        | CP and Host Interaction                             |             |

| 1.3        | Host Resident Block                                 |             |

|            | 1.3.1 Queue Scheduling                              | . 1-4       |

| CHAPTER 2  | PDU Transmission and Reception                      |             |

| 2.1        | PDU Transmission                                    | 2-1         |

| W. 1       | 2.1.1 Tsd Description                               |             |

|            | 2.1.2 Tpd Description                               | . 2-2       |

|            | 2.1.3 Transmit Process                              | . 2-3       |

| 2.2        | PDU Reception                                       |             |

|            | 2.2.1 Receive Buffer Descriptors                    |             |

|            | 2.2.2 Receive Buffer Schemes and Sizes              | 2-6         |

|            | 2.2.4 Buffer Supply Protocol                        |             |

| CHAPTER 3  | Commands                                            |             |

| 3.1        | Activate VCIN Command                               | 3_:         |

| 3.2        | Deactivate VCIN Command                             |             |

| 3.3        | Deactivate VCIO Command                             |             |

| 3.4        | Activate VCIO Command                               |             |

| 3.5        | SUNI OC3 Set Register Command                       |             |

| 3.6        | SUNI OC3 Get Register Command                       |             |

| 3.7        | Statistics Command                                  |             |

| CHAPTER 4  | Initialization                                      |             |

| 4.1        | Downloading the AAL Interface Firmware              | <b>1</b> _1 |

| 1.1        | 4.1.1 Fast Downloading                              |             |

|            | 4.1.2 Notes on the Firmware                         | . 4-2       |

|            | 4.1.3 The Host/CP Endian Description                |             |

| 4.1        | Downloading the AAL Interface Firmware              |             |

| 4.2        | The Cp_queue Structure                              |             |

| 4.0        | 4.2.1 Initialize Queue Pointers                     |             |

| 4.3        | CP Boot Sequence                                    |             |

| 4.4        | Heartbeat - CP State Indication                     | . 4-8       |

| APPENDIX A | DMA Address Alignment                               |             |

| A.1        | Minimum DMA Requirements                            | A-1         |

| APPENDIX B | Host - CP Shared Memory Definitions                 |             |

| B.1        | Memory Offsets                                      | .B-1        |

|            | ·                                                   |             |

| APPENDIX C |                                                     | ~           |

| C.1        | New Functionality                                   |             |

|            | C.1.1 Data Structure                                |             |

|            |                                                     | C-1         |

|            | SBA-200E SBus Slave Interface                       | _           |

| D 1        | SRus Slave Module                                   | D-1         |

| D.2<br>D.3<br>D.4                                                     | Host Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D-2                                                                                                 |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| APPENDIX E                                                            | ESA-200E EISABus Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |

| E.1                                                                   | EISABus Slave Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                     |

|                                                                       | E.1.1 Host Control Register (HCR) E.1.2 High Base Address Register (HBAR) E.1.3 Low Base Address Register (LBAR) E.1.4 Slave Memory Addressing E.1.5 Hold Lock Memory Access E.1.6 Slave Controller Reset                                                                                                                                                                                                                                                                                                                                                                                            | . E-3                                                                                               |

| APPENDIX F                                                            | GIA-200E GIO Bus Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |

| F.1                                                                   | GIOBus Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | F-1                                                                                                 |

| 1.1                                                                   | F.1.1 Processor Identification Word (PIW). F.1.2 Host Control Register (HCR). F.1.3 Host Control Register #2. F.1.4 Adapter Configuration PROM. F.1.5 Local RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                     | . F-1<br>. F-2<br>. F-3<br>. F-3                                                                    |

| APPENDIX G                                                            | PCA-200E PCI Bus Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |

| G.1                                                                   | Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | G-1                                                                                                 |

|                                                                       | G.1.1 Configuration Registers G.1.2 Host Control Register (HCR) G.1.3 Mask Register G.1.4 PCI Specific Register (PSR) G.1.5 Adapter Expansion PROM G.1.6 Local RAM                                                                                                                                                                                                                                                                                                                                                                                                                                   | G-5<br>G-5<br>G-6<br>G-6                                                                            |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                     |

| APPENDIX H                                                            | VMA-200E VME-bus Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |

| APPENDIX H<br>H.1                                                     | VMA-200E VME-bus Slave Interface VMA-200E Pre-Installation Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | H-1                                                                                                 |

|                                                                       | VMA-200E Pre-Installation Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | H-1                                                                                                 |

|                                                                       | VMA-200E Pre-Installation Configuration.  H.1.1 Slave Address Configuration.  H.1.2 VMEbus Short A16 Address Space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | H-1<br>H-2                                                                                          |

|                                                                       | VMA-200E Pre-Installation Configuration.  H.1.1 Slave Address Configuration.  H.1.2 VMEbus Short A16 Address Space.  H.1.3 VMEbus Identification PROM.  H.1.4 Host Control Register.                                                                                                                                                                                                                                                                                                                                                                                                                 | H-1<br>H-2<br>H-3<br>H-3                                                                            |

|                                                                       | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space. H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space.                                                                                                                                                                                                                                                                                                                                                                           | H-1<br>H-2<br>H-3<br>H-3<br>H-4                                                                     |

|                                                                       | VMA-200E Pre-Installation Configuration.  H.1.1 Slave Address Configuration.  H.1.2 VMEbus Short A16 Address Space.  H.1.3 VMEbus Identification PROM.  H.1.4 Host Control Register.                                                                                                                                                                                                                                                                                                                                                                                                                 | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4                                                              |

| H.1                                                                   | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space H.1.6 VMEbus Interrupter H.1.7 VME64 Master Mode.                                                                                                                                                                                                                                                                                                                           | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4                                                              |

|                                                                       | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space. H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register. H.1.5 VMEbus A32 Long Slave Address Space. H.1.6 VMEbus Interrupter. H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface                                                                                                                                                                                                                                                                            | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4                                                              |

| H.1  APPENDIX I                                                       | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space. H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register. H.1.5 VMEbus A32 Long Slave Address Space. H.1.6 VMEbus Interrupter. H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface. Slave Interface. Board Control Register.                                                                                                                                                                                                                                  | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4<br>I-5                                                       |

| H.1  APPENDIX I I.1 I.2 I.3                                           | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space H.1.6 VMEbus Interrupter H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface Slave Interface. Board Control Register Local Memory.                                                                                                                                                                                                                          | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-5<br>. I-1                                                     |

| H.1  APPENDIX I I.1 I.2                                               | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space. H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register. H.1.5 VMEbus A32 Long Slave Address Space. H.1.6 VMEbus Interrupter. H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface. Slave Interface. Board Control Register.                                                                                                                                                                                                                                  | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-5<br>. I-1                                                     |

| H.1  APPENDIX I I.1 I.2 I.3                                           | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space H.1.6 VMEbus Interrupter H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface Slave Interface. Board Control Register Local Memory. Prom Data  SBA-200 SBus Slave Interface                                                                                                                                                                                  | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-5<br>. I-1<br>. I-2                                            |

| H.1  APPENDIX I  I.1 I.2 I.3 I.4  APPENDIX J J.1                      | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space H.1.6 VMEbus Interrupter H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface Slave Interface. Board Control Register Local Memory. Prom Data  SBA-200 SBus Slave Interface Slave Interface.                                                                                                                                                                 | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4<br>H-5<br>. I-1<br>. I-2<br>. I-3                            |

| H.1  APPENDIX I  I.1  I.2  I.3  I.4  APPENDIX J  J.1  J.2             | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space H.1.6 VMEbus Interrupter H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface Slave Interface. Board Control Register Local Memory. Prom Data  SBA-200 SBus Slave Interface Slave Interface. SBus Boot PROM.                                                                                                                                                 | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4<br>H-5<br>. I-1<br>. I-2<br>. I-3<br>. K-1                   |

| H.1  APPENDIX I  I.1 I.2 I.3 I.4  APPENDIX J J.1                      | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space H.1.6 VMEbus Interrupter H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface Slave Interface. Board Control Register Local Memory. Prom Data  SBA-200 SBus Slave Interface Slave Interface.                                                                                                                                                                 | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4<br>H-5<br>. I-1<br>. I-2<br>. I-3<br>. K-1<br>. K-1          |

| H.1  APPENDIX I  I.1  I.2  I.3  I.4  APPENDIX J  J.1  J.2             | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration H.1.2 VMEbus Short A16 Address Space H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space H.1.6 VMEbus Interrupter H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface Slave Interface. Board Control Register Local Memory. Prom Data  SBA-200 SBus Slave Interface Slave Interface. SBus Boot PROM Board Control Register                                                                                                                            | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4<br>H-5<br>. I-1<br>. I-2<br>. I-3<br>. K-1<br>. K-1          |

| H.1  APPENDIX I  I.1 I.2 I.3 I.4  APPENDIX J  J.1 J.2 J.3             | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space H.1.6 VMEbus Interrupter H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface Slave Interface. Board Control Register Local Memory. Prom Data  SBA-200 SBus Slave Interface Slave Interface. SBus Boot PROM Board Control Register J.3.1 Local Memory.  ESA-200 EISA Bus Slave Interface Slave Interface.                                                    | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4<br>H-5<br>. I-1<br>. I-2<br>. I-3<br>. K-1<br>. K-2<br>. K-2 |

| H.1  APPENDIX I  I.1 I.2 I.3 I.4  APPENDIX J  J.1 J.2 J.3  APPENDIX K | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space. H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space H.1.6 VMEbus Interrupter H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface Slave Interface. Board Control Register Local Memory. Prom Data  SBA-200 SBus Slave Interface Slave Interface. SBus Boot PROM Board Control Register J.3.1 Local Memory. ESA-200 EISA Bus Slave Interface Slave Interface. Slave Interface. Slave Interface. Slave Interface. | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4<br>H-5<br>. I-1<br>. I-2<br>. I-3<br>. K-1<br>. K-2<br>. K-2 |

| H.1  APPENDIX I  I.1 I.2 I.3 I.4  APPENDIX J  J.1 J.2 J.3  APPENDIX K | VMA-200E Pre-Installation Configuration. H.1.1 Slave Address Configuration. H.1.2 VMEbus Short A16 Address Space H.1.3 VMEbus Identification PROM. H.1.4 Host Control Register H.1.5 VMEbus A32 Long Slave Address Space H.1.6 VMEbus Interrupter H.1.7 VME64 Master Mode.  MCA-200 Micro Channel Bus Slave Interface Slave Interface. Board Control Register Local Memory. Prom Data  SBA-200 SBus Slave Interface Slave Interface. SBus Boot PROM Board Control Register J.3.1 Local Memory.  ESA-200 EISA Bus Slave Interface Slave Interface.                                                    | H-1<br>H-2<br>H-3<br>H-3<br>H-4<br>H-4<br>H-5<br>. I-1<br>. I-2<br>. K-1<br>. K-2<br>. K-2<br>. K-2 |

| APPENDIX L | GIA-200 GIO Bus Slave Interface     |                          |

|------------|-------------------------------------|--------------------------|

| L.1        | Slave Interface                     | $\dots \dots M\text{-}1$ |

|            | L.1.1 Memory Base Address           | $\dots\dots M\text{-}1$  |

| L.2        | Board Control Register              | M-2                      |

| APPENDIX M | PCA-200 PCI Bus Slave Interface     |                          |

| M.1        | Slave Interface                     | N-1                      |

|            | M.1.1 Configuration Space Registers | N-1                      |

|            | M.1.2 Board control register        | N-3                      |

|            | M.1.3 Serial Number PROM            | N-3                      |

|            | M.1.4 Local memory                  | N-4                      |

|            | M.1.4 Local memory                  | N-4                      |

### **Table of Contents**

# List of Figures

| CHAPTER 1  | Introduction                                             |      |

|------------|----------------------------------------------------------|------|

| CHAPTER 2  | PDU Transmission and Reception                           |      |

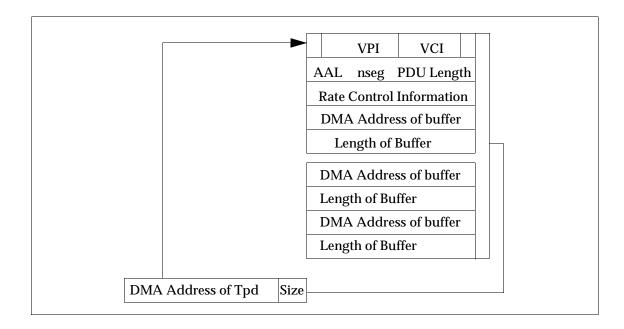

| Figure 2.1 | Transmit PDU Descriptor (Tpd) & Tpd DMA Address Encoding | 2-1  |

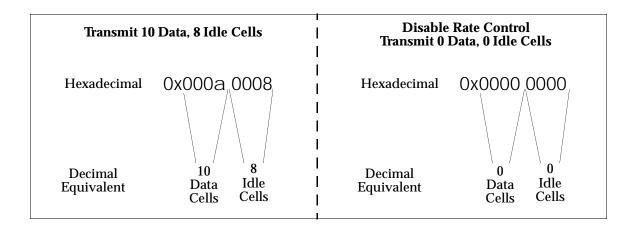

| Figure 2.2 | Rate Control as Data and Idle Cells                      | 2-3  |

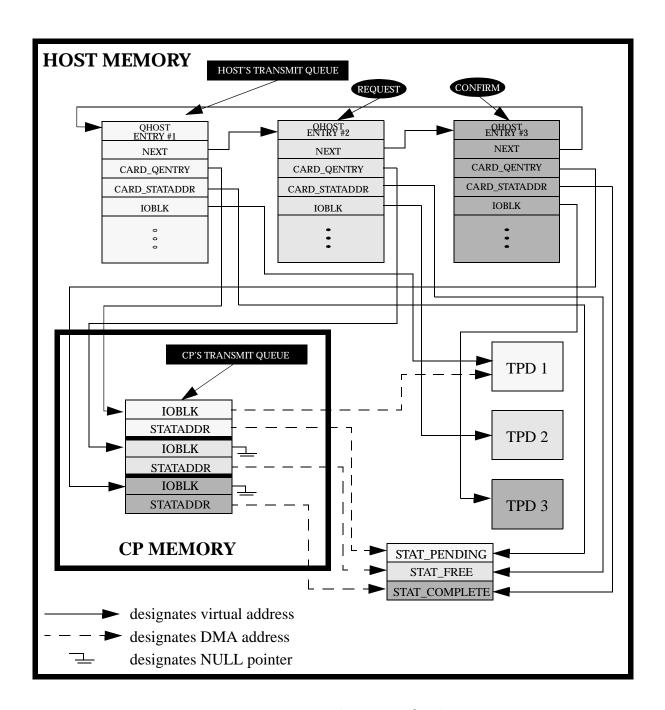

| Figure 2.3 | Transmit Queue Snapshot One                              | 2-4  |

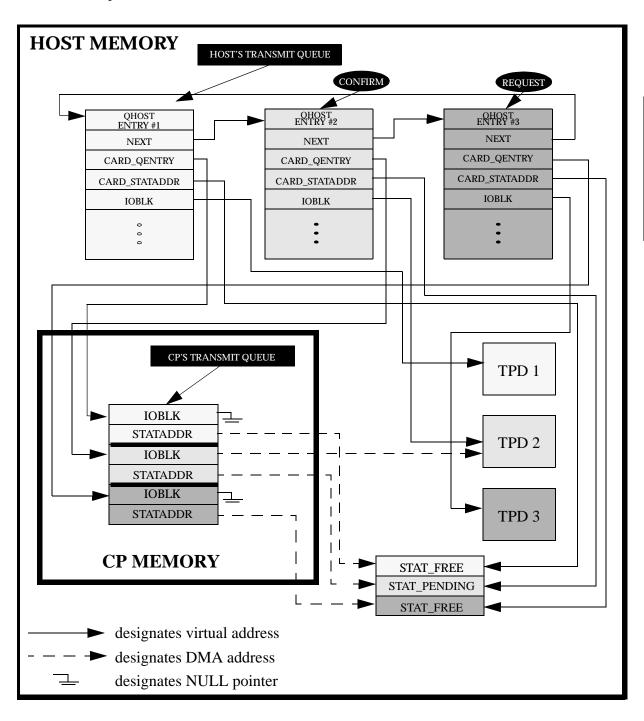

| Figure 2.4 | Transmit Queue Snapshot Two                              | 2-5  |

| Figure 2.5 | Receive Queue                                            | 2-7  |

| Figure 2.6 | Buffer Queue                                             | 2-11 |

| CHAPTER 3  | Commands                                                 |      |

| CHAPTER 4  | Initialization                                           |      |

| Figure 4.1 | Host -CP Shared Memory Offsets                           | 4-5  |

|            |                                                          |      |

# List of Figures

# List of Tables

| Table | A.1 | Minimum DMA Requirements 200 Series Adapters | A-1   |

|-------|-----|----------------------------------------------|-------|

| Table | D.1 | SDC SBus Slave Address Map                   |       |

| Table | D.2 | Host Control Register bit definitions        | D-2   |

| Table | D.3 | SBus Burst transfer configuration register   | D-2   |

| Table | D.4 | SBus Interrupt level selection register      | D-3   |

| Table | E.1 | I/O Address Map for EBI chip                 | E-1   |

| Table | E.2 | Host Control Register bit definitions        |       |

| Table | E.3 | High Base Address Register                   | E-3   |

| Table | E.4 | Low Base Address Register                    | E-3   |

| Table | F.1 | Slave Address Space                          | F-1   |

| Table | F.2 | Host Control Register                        | F-2   |

| Table | F.3 | PROM Address Map                             | F-3   |

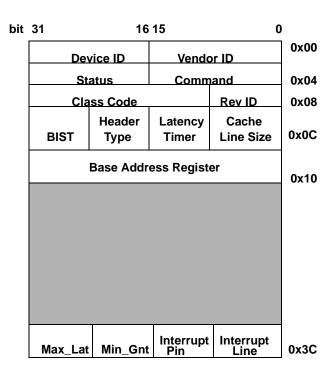

| Table | G.1 | Slave Address Space                          | G-1   |

| Table | G.2 | Configuration Registers                      | G-2   |

| Table | G.3 | PBI Configuration                            |       |

| Table | G.4 | Host Control Register                        | G-5   |

| Table | H.1 | Short Base Address Configuration             | H-2   |

| Table | H.2 | Device Access Decoding Information           |       |

| Table | H.3 | Host Control Register                        | H-3   |

| Table | H.4 | A32 Base Addressing                          | H-4   |

| Table | H.5 | Interrupt Request Level                      | H-5   |

| Table | H.6 | VME64 Master Mode Selector                   | H-5   |

| Table | I.1 | I/O Space                                    | . I-1 |

| Table | I.2 | Board Control Registers                      | I-2   |

| Table | I.3 | PROM Attributes                              | I-3   |

| Table | I.4 | PROM Contents                                | I-4   |

| Table | K.1 | Slave Interface Addresses                    | K-1   |

| Table | K.2 | Board Control Registers                      | K-2   |

| Table | L.1 | Slave Access Address Map                     | .L-1  |

| Table | L.2 | EISA Base Address for the i960 RAM           | .L-3  |

| Table | L.3 | Memory Base Address Register, High Slice     | .L-3  |

| Table | L.4 | Memory Base Address Register, Low Slice      | .L-3  |

| Table | L.5 | Board Control Registers                      |       |

| Table | M.1 | Slave Interface Addresses                    | M-1   |

| Table | M.2 | Board Control Registers                      | M-2   |

| Table | N.1 | Board Control Registers                      | N-3   |

# List of Tables

# **Preface**

# **Technical Support**

If your equipment is under warranty or a support contract with FORE Systems, please reference the following information for technical support issues.

In the U.S.A., you can contact FORE Systems' Technical Support by any one of four methods:

1. If you have access to Internet, you may contact FORE Systems' Technical Support via E-Mail at the following address:

### support@fore.com

2. You may FAX your questions to "support" at:

412-742-7900

3. You may send questions, via U. S. Mail, to the following address:

FORE Systems, Inc. 1000 FORE Drive Warrendale, PA 15086-7502

4. You may telephone your questions to "support" at:

1-800-671-FORE(3673)

or

412-635-3700

Technical support for non-U.S.A. customers should be handled through your local distributor.

When contacting Technical Support, please be prepared to provide you customer support ID number, the serial number(s) of the product(s) and as much information as possible describing your problem or question.

# **Typographical Styles**

Throughout this manual, specific commands to be entered by the user appear on a separate line in bold typeface. In addition, use of the Enter or Return key is represented as <ENTER>. The following example demonstrates this convention:

#### cd /usr/FORE <ENTER>

Commands, parameters, menu items, or file names that appear within the text of this manual are represented in the following style: "...the Configure button will access the next menu item."

As in the following example, any messages or code appearing on a screen will appear in Courier font to distinguish this text from the rest of the text.

.... Are all four conditions true?

# **Important Information Indicators**

To call your attention to safety and otherwise important information that must be reviewed to ensure correct and complete installation, as well as to avoid damage to the adapter or your system, FORE Systems utilizes the following *WARNING/CAU-TION/NOTE* indicators.

**WARNING** statements contain information that is critical to the safety of the operator and/or the system. Do not proceed beyond a **WARNING** statement until the indicated conditions are fully understood or met. This information could prevent serious injury to the operator and/or damage to the adapter, the system, or currently loaded software, and will be indicated as:

#### **WARNING!**

Hazardous voltages are present. To lessen the risk of electrical shock and danger to personal health, follow the instructions carefully.

Information contained in **CAUTION** statements is important for proper installation/operation. Compliance with **CAUTION** statements can prevent possible equipment damage and/or loss of data and will be indicated as:

#### **CAUTION**

You risk damaging your equipment and/or software if you do not follow these instructions.

Information contained in **NOTE** statements has been found important enough to be called to the special attention of the operator and will be set off from the text as follows:

### NOTE:

Steps 1, 3, and 5 are similar to the installation for the computer type above. Review the previous installation procedure before installation in your particular model.

Preface

#### Introduction 1.1

This document specifies an ATM Adaptation Layer Interface (AALI) for host device drivers and signaling protocol modules. The AALI is a programming interface which is built upon the FORE Systems 200-series hardware, specifically, the on-board RAM and the board control register (BCR).

This document refers to a 200-series adapter and the firmware executing on the 200series as the cell processor (CP).

#### 1.1.1 **Overview**

The CP implements the AAL4 and AAL5 protocol standards. A null AAL interface is also available, providing access to the ATM layer. This interface allows complete 53byte ATM cells to be transferred to and from the host.

Communication between the host processor and the CP is primarily through shared CP memory and host memory. CP to host interrupts can also be enabled. The CP accesses host memory using bus master direct memory access (DMA). The host uses memory-mapped accesses to write the CP memory and the BCR. The CP memory only supports 32-bit word accesses.

The CP is capable of scatter/gather DMA, allowing the host buffers to be discontiguous. The buffer descriptors allow cell-payloads to be transferred to and from the host operating systems' native network buffers. The CP does not buffer cell-payloads in CP memory, instead they are transferred to and from the network using fly-by DMA.

#### **CAUTION**

This document describes a specific version (1.8) of the AALI firmware. The driver developer is cautioned that the versions of header files that are being used to build a driver must match the version of the AALI firmware that is being used.

#### 1.2 CP and Host Interaction

A series of CP resident queues are used by the host to initiate operations:

- PDU receive queue

- PDU transmit queue

- · Command queue

- Receive buffer supply queues

Queue accesses by the host are limited to a single write-only access per operation. For example, to transmit a PDU, the host writes a single pointer to the tail of the transmit queue. Host to CP interrupts are not used to notify the CP of a host-initiated operation, instead the CP polls each queue head.

Two types of queues exist. They differ only in the location of the (I/O block). The transmit, receive and buffer supply queues reference a host resident I/O block, while the command queue has a CP resident I/O block.

All queues reference a location in host memory where a queue status entry is maintained. The host initializes the status word before initiating an operation and the CP overwrites the status word on completion. The host uses the value of the status word to determine if an operation has completed and whether a queue is full or not-full before initiating an operation. The status word must be four byte aligned in host memory.

The CP writes stat\_complete to the status word on completion and may logically or stat\_error with stat\_complete if an error has occurred (i.e. (stat\_complete | stat\_error)).

### 1.3 Host Resident Block

The transmit, receive and buffer supply queues have a host resident I/O block. For these three types of queues, a single queue entry has the following structure:

The ioblock member can reference a transmit PDU descriptor (Tpd), a receive PDU descriptor (Rpd) or a receive block descriptor (Rbd) located in host memory. The stataddr member references a location in host memory where the CP can write completion status. Both the ioblock and stataddr members reference a location in host memory. This address must be accessible from the CP side of the hosts I/O bus via DMA.

Below is a general description of CP and host interaction. See the section on specific queue types for more details.

- The host maintains a host resident tail pointer to each queue and the CP maintains a CP resident head pointer. For each CP resident queue entry, the host must maintain a host resident status word. Each queue wraps around from the end to the beginning forming a logical ring.

- For each queue entry, the host initializes the host resident status word to stat\_free. The host then writes the stataddr member of the CP resident queue entry with the DMA address of that status word. This should be done only once at initialization (i.e. the value of the stataddr member remains constant).

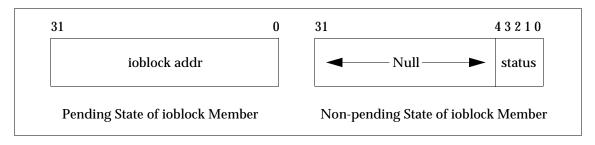

- To initiate an operation, the host first initializes the host resident status word to stat\_pending and then writes the ioblock member of the queue entry with the DMA address of the host resident I/O block. The host then advances its head pointer. It is the act of writing the I/O block entry with a new address that signals to the CP that the queue entry is ready for processing.

The CP notices that the ioblock member of the queue entry has changed and starts the operation associated with that queue. At the end of the operation, the CP will zero the ioblock member of the queue entry. It will then overwrite the status word with stat\_complete using the DMA address found in the stataddr member of the queue entry. If the queue is the receive queue or a command queue and interrupts are not masked then the host is interrupted.

NOTE:

The CP zeros the ioblock member of the queue entry to recognize a queue empty condition. The host should never read CP memory to determine when the CP has completed an operation but should read the host resident status word. This CP action is documented only to aid in host device driver debugging.

### 1.3.1 Queue Scheduling

In addition to the various shared memory queues the CP also examines the network receive FIFO for available cells. The receive FIFO is treated as yet another queue by the CP. The receive FIFO is 16K deep and can hold up to 290 host formatted cells.

If cells are available then some number of cells are transferred to host memory before scanning the other queues.

The CP queues are serviced in the following order:

- 1. Buffer resupply queue

- 2. Network cell receive queue

- 3. PDU transmit queue

- 4. Host command queue

#### **PDU Transmission** 2.1

The host transmits a PDU by first initializing a host resident transmit PDU descriptor (Tpd), then setting the host resident status word to stat\_pending and finally writing the transmit queue with the DMA address of the Tpd.

The size of a Tpd must be a multiple 32 bytes and be aligned on a 32 byte boundary. The least significant 5 bits of the DMA address are used by the host to encode the size of the Tpd in 32 byte blocks. See Figure 2.1.

Figure 2.1 - Transmit PDU Descriptor (Tpd) & Tpd DMA Address Encoding

For each PDU segment, data buffering addresses and lengths are encoded in a Tsd. The host must ensure that data for each segment starts on a 32-bit word address and that the length of each segment is a multiple of four bytes.

#### 2.1.1 **Tsd Description**

Each PDU segment is described by a Tsd.

```

struct transmit_segment {

Haddr buffer;

/* transmit buffer DMA address */

length;

/* number of bytes in buffer */

typedef struct transmit_segment Tsd;

```

## 2.1.2 Tpd Description

The entire PDU to be transmitted is described by a Tpd. The first word of the Tpd contains the VC used to transmit this PDU.

The first four bytes of the <code>Tpd</code> (atm\_header) are a representation of the ATM Header that will be used to transmit cells for the PDU. It is in the form of a standard ATM Header minus the HEC byte. The fields of this header used during PDU transmission are the VPI and VCI fields.

```

Tsd specification (spec) word format:

* 31 28 24 23 16 15 8 7 0

* +---+

|intr|aal|num seg |

+---+

\star Transmit ioblock member encoding (the tpd

dma address written to the transmit queue).

5 4 3 2 1 0

+----+

ioblock addr |R|

_____

* R = reserved (zero)

N = size of Tpd in 8 word blocks

struct tx_pd {

u_int atm_header;

u_int spec;

u_int rc_stream_desc;

/* Number of data cells/interval */

u_int pad;

segment[NUM_TXSEG];

Tsd

typedef struct tx_pd Tpd;

```

#### 2.1.3 Transmit Process

When issuing a transmit the host checks the status of any previous transmit requests by examining the host resident status word associated with that request for the value stat\_complete. If complete, the host can free host resources used for the transmitted PDU. One factor in determining the transmission speed is rate control.

Rate control information is encoded as a thirty-two bit field comprised of two sixteen bit sub-fields which form a ratio of data cells to idle cells. The high order sixteen bits represent the number of data cells to send, and the low order sixteen bits specify the number of idle cells. For example, a value of 0x000a0008 instructs the firmware to transmit ten data cells and eight idle cells per eighteen cells (shown graphically in Figure 2.2). Specifying 0x0 for both sixteen bit fields disables the rate-control mechanism. Rate control is applied on a per-TPD basis.

Figure 2.2 - Rate Control as Data and Idle Cells

Figure 2.3 depicts a 3-element transmit queue where the host has issued a transmit for Tpd 3, advanced the request pointer, issued a transmit for Tpd 1, and advanced the request pointer again. The CP has transmitted the PDU referenced by Tpd 3 and Tpd 1 is still pending.

As you can see, the host has a queue which is needed to keep track of the queue the CP references to emit PDUs. The host transmit queue is set up during initialization to contain pointers to all the relevent pieces of data, of each transmit element. For each QHOST element, there is an associated Tpd, a pointer to a corresponding QCARD element (which exists on the transmit queue of the CP), and a pointer to the status word element (host-resident in this example). Once these essential pieces are set up, no reallocation is performed; i.e., each free Tpd can be thought of as a fixed sized container, holding PDU information. When the Tpd container has been filled, the status word for that Tpd is set to STAT\_PENDING, and the DMA address of the Tpd is transferred to the CP's transmit queue. When this DMA address is set, the CP will then recognize that the host has given another PDU for transmit. (Note that the status word DMA addresses within the CP's transmit queue are never changed after initialization.)

Figure 2.3 - Transmit Queue Snapshot One

Figure 2.4 shows the state of the transmit queue after the CP has transmitted  $Tpd\ 1$  and the host has cleaned up after  $Tpd\ 3$  and  $Tpd\ 1$ , advancing the confirmation pointer twice. The host has also issued a transmit for  $Tpd\ 2$  advancing the request pointer once.

Figure 2.4 - Transmit Queue Snapshot Two

## 2.2 PDU Reception

The host enables PDU reception by initializing the receive queue, supplying the CP with buffers and activating a VCI (i.e. opening an ATM connection).

The CP carries out the reassembly of cells into a PDU, buffering the cell-payloads in host memory. For each partially reassembled PDU, the CP maintains a CP resident copy of a receive PDU descriptor (Rpd). An Rpd specifies the VPI/VCI, PDU length and buffers comprising a PDU. The CP copy of the Rpd is initialized by the CP during the reassembly process. When the last cell of a PDU is transferred to host memory, then the Rpd is also transferred to host memory and the host is interrupted.

For connections with an AAL of type null, cell payloads will be written contiguously into the reassembly buffers. For this AAL type, the CP implements header coalescing, where cells arriving with identical headers are grouped together and delivered to the host as a batch. The maximum number of cells in a group is controlled by the MTU (or batch size) for that connection. So the net effect is that the host is notified that cells have arrived on an AAL null connection only when either a cell arrives on that connection with a different header, or the number of cells which have arrived equals the current batch size.

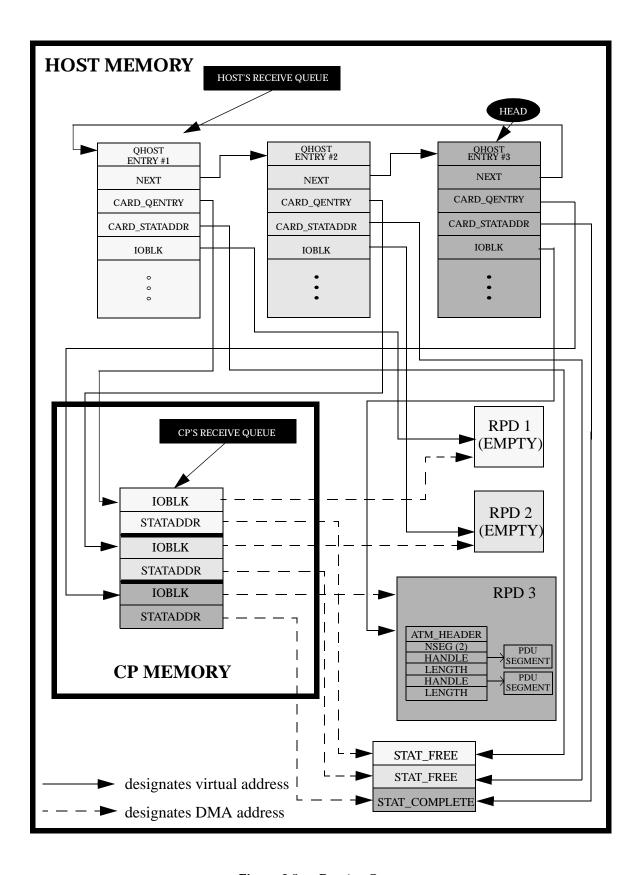

Each entry of the receive queue is initialized by the host to reference a location in host memory equal to the size of an Rpd. This location can be viewed as a fixed sized container supplied by the host containing uninitialized values. The Rpd container will eventually hold an initialized Rpd put there by the CP. See Figure 2.5.

As with the transmit queue paradigm, PDU reception is accomplished via the interaction of a CP receive queue and its counterpart within the host driver. Each QHOST entry within the host's receive queue contains pointers to pairings of status words and Rpd structures. When a status word is set to STAT\_COMPLETE, the corresponding Rpd contains a PDU that has been received by the CP; otherwise, the status word isn't set to completion and the Rpd is empty.

Figure 2.5 - Receive Queue

The length of the receive queue is configurable by the host and represents the maximum number of PDUs that can be queued for the host before the CP starts discarding cells.

The host maintains a host resident head pointer to the receive queue and the CP maintains a CP resident tail pointer to the receive queue.

A receive PDU interrupt indicates that one or more PDUs are ready to be processed by the host. The host need only check the head of queue status word for the value stat\_complete. After processing a PDU, the host must then make a new Rpd container available to the CP by re-writing the receive queue with the DMA address of the same or a new Rpd container.

### 2.2.1 Receive Buffer Descriptors

The CP can support multiple host buffer schemes (e.g. BSD mbuf, System V STREAM buffer, frame buffer, etc.) through a host buffer independent buffer descriptor. The buffer descriptor gives the CP a uniform view of all host buffer schemes.

A receive buffer descriptor contains two parts, referencing the same host buffer structure. One part is the DMA address used by the CP for writing cell-payloads to host memory. The second part is a handle which is used by the host CPU to locate the buffer while processing a received PDU. The handle part migrates from the host supplied buffer descriptor to a receive PDU descriptor. It is simply passed along during the reassembly process, uninterpreted by the CP.

```

struct receive_buffer_descriptor {

Haddr handle;    /* host CPU control address of buffer */

Haddr buffer;    /* DMA address of host buffer */

};

typedef struct receive_buffer_descriptor Rbd;

```

### 2.2.2 Receive Buffer Schemes and Sizes

The CP maintains a buffer pool for each buffer scheme and buffer size (for example, number of pools = number of schemes \* number of magnitudes). For each connection opened, the host specifies which buffer scheme the CP must use to buffer the cell-payloads for incoming cells.

The binding of a particular buffer scheme (Bscheme) to a particular host buffer scheme is done by the host with the activate command. The CP has no knowledge of the binding. For example bscheme\_one may be bound to BSD mbufs or System V STREAMs buffers.

Host buffer schemes

The firmware has a uniform view of all host buffer schemes through the buffer descriptors. (e.g. Bscheme may be designated by the host to be an mbuf/loaned mbuf. a streams buffer etc.)

```

enum buffer_scheme {

bscheme_one = 0,

bscheme_two = 1

};

typedef enum buffer scheme Bscheme;

```

Within each host buffer scheme, the CP will optionally support multiple buffer magnitudes. Currently small and large buffers are supported. The host chooses the length of small buffers and large buffers with the initialize command. All buffers for a particular

buffer scheme and magnitude must be the same size. It is recommended that for efficiency reasons these be a multiple of 48 bytes.

**Host buffer magnitude** What is designated to be small or large by the host is arbitrary. (They can be equal).

The use of small buffers can be disabled by the host at initialization. If small buffers will be used, then the CP allocates one to hold the first cell-payload of a new PDU. If the remaining cells of the PDU will not fit into the original small buffer, then large buffers are used to complete the reassembly process.

If the CP runs out of small buffers for first cell-payload processing, then it will attempt to allocate a large buffer. However, if the CP has made the transition from using small buffers to large buffers and then runs out of large buffers, it will not attempt to allocate small buffers, instead the PDU reassembly process is aborted.

## 2.2.3 Receive PDU Descriptors

Receive PDU descriptors (Rpd) reside in host memory. They are supplied by the host and used by the CP. An Rpd can be in one of two states; empty or not-empty. When empty, it can be viewed as a fixed size container supplied by the host containing uninitialized values. In the not-empty state, the Rpd has been initialized by the CP (DMA write) with values that describe a received PDU.

The size of an Rpd is fixed at eight 32-bit words (3 receive segments). The host can extend the size of an Rpd with the initialize command in increments of eight 32-bit words (4 receive segments). The extension is based of the size of host buffers and the MTU size. For example, if the largest MTU accepted is 9180 bytes and a small buffer is 256 bytes and a large buffer is 4K, then the Rpd would have to be extended.

For example:

$$(256 + 2 \times 4K) < 9180$$

Therefore, 3 receive segments would be insufficient.

```

struct rx_pd {

u_int atm_header;

int nseg;

Rsd segment[NUM_RXSEG];

};

typedef struct rx pd Rpd;

```

The receive segment descriptor (Rsd) describes a segment of a received PDU. The handle part is used by the host to locate the host buffer while processing a received PDU. The handle is passed along by the CP from a host supplied receive buffer descriptor (Rbd) to the Rsd.

```

struct receive_segment {

Haddr handle; /* receive buffer handle */

int length; /* number of bytes in buffer */

};

typedef struct receive_segment Rsd;

```

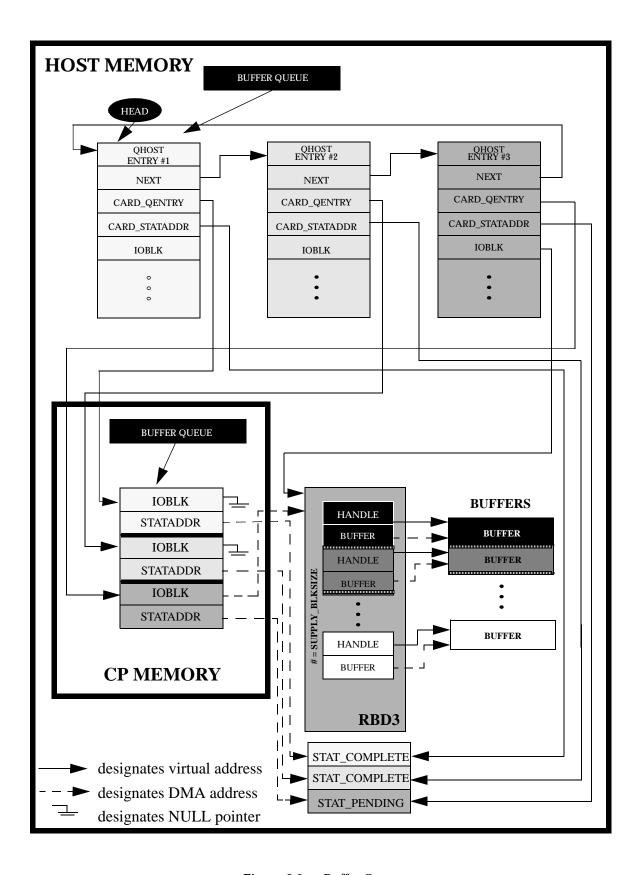

### 2.2.4 Buffer Supply Protocol

For each buffer scheme and magnitude, there is a supply queue and a CP resident buffer descriptor pool (see Figure 2.6). The host supplies the new buffer descriptors to the CP in fixed size blocks of buffer descriptors. The ioblock member of the queue entry points to an area in host memory that contains a fixed number of Rbd's.

If there are entries in particular buffer supply queue and the CP has space in the corresponding descriptor pool, the CP will transfer the block of descriptors to that pool. The CP then notifies the host that it has read the set of Rbd's by writing stat\_complete to the host status word associated with that buffer resupply queue entry.

This protocol allows the CP to maintain a group of usable buffer segments in an area that is quickly accessible to it while allowing the host to supply the CP with more descriptors when convenient (e.g. in the host interrupt routine and/or when transmitting a PDU).

The length of each supply queue and the number of descriptors per block are configurable by the host with the initialize command. The supply queue and transmit queue function identically with the exception that the ioblock member references a host resident supply block instead of a Tpd.

Figure 2.6 - Buffer Queue

The command queue is slightly different than the other queues. Instead of the queue entry referencing an I/O block in host memory, the I/O block is located within the command queue. The host writes the command arguments directly to the queue entry. Each command queue entry has the following structure:

```

union command {

Opcode

op;

Activate_block

activate_param;

Deactivate_block

deactivate_param;

Request stats

stats_param;

Oc3_reg_op

oc3_reg_param;

int force_multiple4[4]; /* gcc960 does this */

};

typedef volatile union command Command;

struct command_block {

Command cmd;

Haddr stataddr;

int force_multiple4[3]; /* gcc960 does this */

};

typedef volatile struct command_block Qcard_cmd;

```

The host issues commands by first writing the command arguments into the queue entry at the head of the queue and then by writing the opcode. The order is important because the CP polls the op location within the command block in order to detect the presence of a new command. When an opcode is detected, the command arguments are assumed to be valid. On command completion, the CP notifies the host by writing stat\_complete to the host status word (stataddr). The host can request that the CP interrupt the host on command completion. Any opcode can be modified with the opcode modifier op\_interrupt\_sel by logically ORing it with an opcode (e.g. (op\_activate | op\_interrupt\_sel).

After completion of a command, the CP zeros the op member of a command queue entry in order recognize a queue empty condition. This is documented to aid in device driver development. The host should not read CP memory to determine when the CP has completed a command but should either request an interrupt or read the host resident status word.

```

* Command opcodes.

* /

enum opcodes {

op initialize

= 0x01, /* init 200-series

* /

= 0x02, /* activate incoming VCI

op_activate_vcin

* /

op_activate_vcout = 0x03, /* activate outgoing VCI

* /

op_deactivate_vcin = 0x04, /* deactivate incoming VCI

* /

op_deactivate_vcout = 0x05, /* deactivate outgoing VCI

* /

= 0x06, /* return AAL and buffer stats

op request stats

* /

= 0x07, /* modify SUNI OC3 register

* /

op_oc3_set_reg

op_oc3_get_reg

= 0x08, /* return SUNI OC3 registers

* /

= 0x09, /* zero card statistics

op_zero_stats

* /

= 0x0a, /* return expansion rom info

op get prom data

* /

op_setvpi_bits

= 0x0b /* set x bits of those decoded by*/

/* the firmware to be low order

/* bits from the VPI field of the*/

/* ATM cell header.

* /

= 0x80 /* interrupt select

* /

op_interrupt_sel

};

typedef volatile enum opcodes Opcode;

```

The "op\_get\_prom\_data" command is specific only to a PCI card implementation.

### 3.1 Activate VCIN Command

This command is used by the host to open an incoming ATM connection. Once a connection is opened, the CP will start reassembling cells having opened the vpvc into PDUs.

The vpvc is used by the host to specify the VPI and VCI to be used for the connection. The VPI must be zero. The VCI must be in the range of zero to the number of connections supported. The host uses the initialize command to select the number of connections supported.

The host also selects the AAL for the incoming cell stream and the buffer scheme to be used to buffer cell-payloads during the reassembly process.

For AAL null connections, the MTU is the amount of data (in bytes) that should be received before notifying the host. Since AAL null cells are grouped into batches and then delivered to the host, the MTU is alternatively referred to as the batch size.

The batch size of an AAL null connection may be changed while the connection is open by simply issuing another Activate VCIN command and specifying a new MTU. Issuing an Activate VCIN command for a connection which is already open is only permitted for AAL null connections.

```

/*

Activate VCI; used by the host to enable the reassembly

of cells with the specified VCI. Op word format:

31

24 23

16 15

8 7

+----+

|reserved| bscheme|

aal | opcode |

+----+

* /

struct activate_block {

Opcode op;

Vpvc

vpvc;

u int

mtu; /* For AAL null only */

};

typedef volatile struct activate block Activate block;

```

## 3.2 Deactivate VCIN Command

This command is used by the host to close an incoming ATM connection. Cells which arrive for the specified VCI after the connection is closed are discarded.

```

/*

* Deactivate VCI command block.

*/

struct deactivate_block {

Opcode op;

Vpvc vpvc;

};

typedef volatile struct deactivate_block Deactivate_block;

```

## 3.3 Deactivate VCIO Command

This command is reserved for future use.

## 3.4 Activate VCIO Command

This is command is reserved for future use.

# 3.5 SUNI OC3 Set Register Command

This command is used by the host to set the value of a SUNI OC3 register (see PMC-Sierra, Inc. PM5345 SUNI Saturn User Network Interface).

The oc3\_op field of Oc3\_reg\_op differs from other firmware commands with opcodes in that oc3\_op is used to encode more information than just the specified operation. This field is used to encode a mask, value and register as well as the intended operation.

To alter the value of a SUNI register, the host must set <code>opcode</code> to <code>op\_oc3\_set\_reg</code> and <code>reg</code> to the appropriate SUNI OC3 register number (refer to comment titled 'OC3 Register Command'). Both the <code>value</code> and mask fields must also be set in the following way:

The mask field specifies which bits of the value field are interpreted by the firmware. For example, if only the least significant two bits of a write to reg should be modified, set mask to 0x3.

The value field specifies the logical value to place at each bit position of reg that mask states is interpreted. This scheme facilitates the setting of specific bit positions within each register without the need to read, modify, then write the specified register.

The oc3\_buff field is unused for a set operation.

```

/*

* OC3 Register Command: used by the host to get/set specific

SUNI register values. Op word format:

24 23

16 15

8 7

+----+

| mask | value | reg | opcode |

+----+

struct oc3_reg_op {

Opcode

oc3 op;

Oc3_reg_set200 *oc3_buff; /* DMA address of oc3 buffer */

};

typedef volatile struct oc3_reg_op Oc3_reg_op;

struct oc3_reg_set200 {

u_int reg[128];

};

typedef struct oc3_reg_set200 Oc3_reg_set200;

```

#### **SUNI Write Example:**

Set the two high order bits of SUNI reg 0x34 to 0, not altering the low order 6 bits.

```

mask = 0xC0 (high order 2 bits set to 1)

value = 0x00 (high order 2 bits set to 0)

reg = 0x34

opcode = op_oc3_set_reg

```

For example, only consider the two high order bits of value when writing to register 0x34 leaving the other 6 bits alone, and the value of these two bits are 0.

## 3.6 SUNI OC3 Get Register Command

This command is used by the host to retrieve the value of SUNI OC3 registers (see PMC-Sierra, Inc. PM5345 SUNI Saturn User Network Interface).

To retrieve the value of the SUNI registers, the host must set opcode to op\_oc3\_get\_reg. The reg, value, and mask fields are not interpreted.

All registers are returned into the buffer pointed to by oc3\_buff. Unimplemented registers will have the value -1. oc3\_buff must be 32 byte aligned.

```

* OC3 Register Command; used by the host to set and

* retrieve SUNI OC3 register values. Op word format:

31

24 23

16 15

8 7

+----+

mask | value | reg | opcode |

+----+

* /

struct oc3_reg_op {

Opcode

oc3_op;

Oc3_reg_set200 *oc3_buff; /* DMA address of oc3 buffer */

};

typedef volatile struct oc3_reg_op Oc3_reg_op_t;

struct oc3_reg_set200 {

u_int reg[128];

};

typedef struct oc3_reg_set200 Oc3_reg_set200;

```

## 3.7 Statistics Command

This command causes the CP to transfers the contents of the CP resident Atm\_stats structure to host memory. The stats\_buff structure must be thirty-two byte aligned in host memory.

```

/*

* Request statistics command block.

struct request_stats {

Opcode

op;

Haddr

stats buff; /* DMA address of stats buffer */

};

typedef volatile struct request_stats Request_stats;

* Statistics.

* /

struct phy_4b5b_stats200 {

crc header errors; /* cells with bad header CRC */

u long

/* cells with bad framing */

u_long

framing_errors;

/* pad to gcc960 boundary */

u long

pad[2];

};

typedef struct phy 4b5b stats200 Phy 4b5b stats200;

/* OC3 PHY */

struct phy oc3 stats200 {

u int section bip8 errors;/* section 8 bit interleaved parity */

u_int path_bip8_errors; /* path 8 bit interleaved parity */

u int line bip24 errors; /* line 24 bit interleaved parity */

u int line febe errors; /* line far end block errors */

u_int path_febe_errors; /* path far end block errors */

/* correctable header check sequence */

u_int corr_hcs_errors;

u_int ucorr_hcs_errors; /* uncorrectable header check sequence */

/* pad to gcc960 boundary */

u_int

pad[1];

};

typedef struct phy_oc3_stats200 Phy_oc3_stats200;

struct atm_stats200 {

/* ATM layer */

cells_transmitted; /* cells transmitted */

u long

u long cells received;

/* cells received */

u_long vpi_bad_range;

/* cell drops: VPI out of range */

/* cell drops: no conn for VPI */

u_long vpi_no_conn;

/* cell drops: VCI out of range */

u long vci bad range;

u_long vci_no_conn;

/* cell drops: no conn for VCI */

```

```

/* pad to gcc960 boundary */

u_long

pad[2];

};

typedef struct atm_stats200 Atm_stats200;

/* Null AAL */

struct aal0_stats200 {

/* cells transmitted */

u_long

cells_transmitted;

/* cells received */

u_long

cells_received;

/* cells dropped */

u_long

cells_dropped;

/* pad to gcc960 boundary */

u_long

pad[1];

};

typedef struct aal0_stats200 Aal0_stats200;

struct aal4_stats200 {

/* AAL4 */

/* cells xmited from PDUs */

u_long

cells_transmitted;

/* cells assembled in PDUs */

u_long

cells_received;

/* payload CRC error count */

u_long

cells_crc_errors;

cells_protocol_errors; /* SAR or CS layer errors */

u_long

u_long cells_dropped;

/* cells dropped */

/* CS PDUs transmitted */

u_long cspdus_transmitted;

/* CS PDUs received */

u_long

cspdus received;

cspdus_protocol_errors;/* CS layer protocol errors */

u_long

u_long

cspdus_dropped;

/* PDUs dropped (in cells) */

u_long

pad[3];

/* pad to gcc960 boundary */

};

typedef struct aal4_stats200 Aal4_stats200;

/* AAL5 */

struct aal5_stats200 {

u_long

cells_transmitted; /* cells transmitted from SDUs */

/* cells reassembled into SDUs */

u_long

cells_received;

congestion_experienced; /* CRC err & length wrong */

u_long

/* PDUs dropped (in cells) */

u_long

cells_dropped;

cspdus_transmitted;/* CS PDUs transmitted */

u_long

/* CS PDUs received */

u_long

cspdus_received;

u_long

cspdus_crc_errors; /* PDU CRC errors */

cspdus_protocol_errors; /* CS protocol errors */

u_long

u long

cspdus dropped;

/* reassembled PDUs dropped */

u_long

pad[3];

/* pad to gcc960 boundary */

};

typedef struct aal5 stats200 Aal5 stats200;

struct auxiliary_stats200

u long

small_b1_failed;

/* rcv BD allocation failures */

large b1 failed;

/* rcv BD allocation failures */

u long

```

```

/* rcv BD allocation failures */

small_b2_failed;

u_long

u_long

large_b2_failed;

/* rcv BD allocation failures */

u_long

rpd_alloc_failed; /* rcv PDU allocation failures */

receive_carrier;

/* no carrier = 0, carrier = 1 */

u_long

/* pad to gcc960 boundary */

u_long

pad[2];

};

typedef struct auxiliary_stats200 Auxiliary_stats200;

struct stats200 {

Phy_4b5b_stats200 phy4b5b;

Phy_oc3_stats200

phyoc3;

Atm_stats200

atm;

Aal0_stats200

aal0;

Aal4_stats200

aal4;

Aal5_stats200

aa15;

Auxiliary_stats200 aux200;

};

typedef struct stats200 Stats200;

```

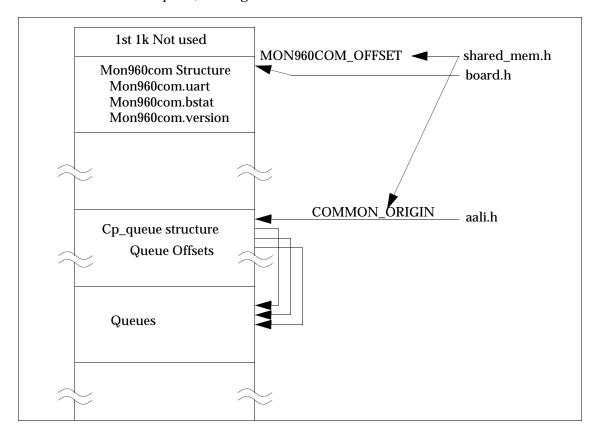

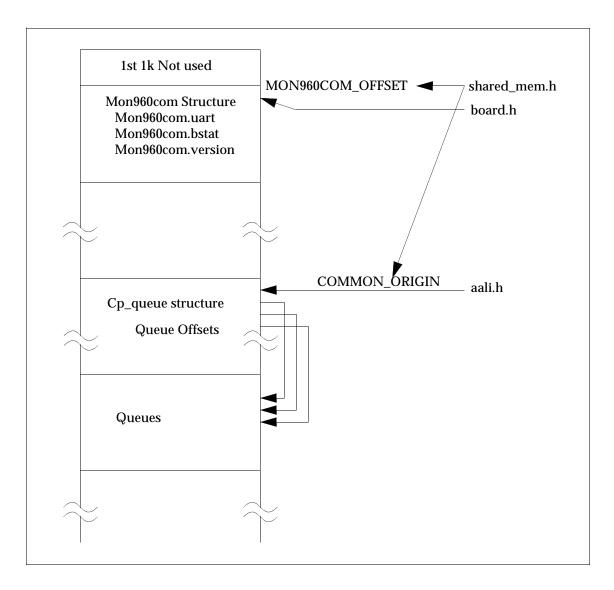

This chapter provides some details on how the CP is loaded with the AAL interface firmware and how that firmware is initialized.

#### **Downloading the AAL Interface Firmware** 4.1

Firmware images can be loaded using one of two methods. In the past (refer to any ForeThought 4.0.x source distribution for more details), FORE's drivers used a virtual terminal interface to download the firmware through shared memory, byte by byte. Briefly, after executing a series of self-tests the CP starts to execute a version of the mon960 program from Intel. This software interacts with a "terminal" through a "UART" (Universal Asynchronous Transmitter/Receiver). In the case of the FORE CP, that UART is the soft uart implemented through shared memory.

To download a program onto the CP, a do command is sent to the CP over the soft uart. This command instructs the mon960 program to accept a new executable image. This image must be in b.out or Common Object File Format (COFF) format, and is sent to the CP using the xmodem protocol--firmware images used in this method use a .ucode extension. During the transmission, the format is translated to stripped COFF format. After successful completion, mon960 is sent the 90 command. The CP will then begin execution at the address provided as a parameter to this command.

The faster method, used by ForeThought 4.1 drivers, is to load the firmware directly into the adapter card's RAM--it was originally designed for use within the PC drivers. In this case, no translations are necessary (beyond dealing with the "endianness" of the target processor). Its method is implemented in a utility called norm, and is described next.

## 4.1.1 Fast Downloading

A .bin file is a firmware image file that begins with a four word header, which defines the following: a firmware identification number, its version, the offset from the top of RAM where the firmware is to be loaded, and the entry point for the firmware. Loading a .bin file into a FORE adapter card's RAM requires essential three steps:

Read the top four words into a data structure so that these values may be used during the download procedure:

```

struct {

/* 0x65726f66 ==> "fore" */

u_int32_t firmId;

u int32 t firmVersion ID;

u_int32_t startOffset;

u_int32_t entryAddr;

} firmHeader;

int headSize = sizeof(firmHeader);

handle= OPEN(<device>.bin, "r");

error= READ FILE (handle, &firmHeader, headSize);

```

Any error checking can be done next using the first two fields in the header. Note that the header is part of the image, and therefore must also be downloaded to the card.

• Transfer the header just read and the rest of the image into the card's memory, starting at the offset given in the header:

```

startP= au->au_ram + firmHeader.startOffset;

error = COPY(startP, &firmHeader, headSize);

iSize = firmSize - headSize;

error = READ FILE(handle, startP+headSize, iSize);

```

Because the host and the I960 may have different byte orderings, a reordering

of the entire file may be necessary. Specifically, big-endian hosts require a

reordering of each word because the file is read as bytes and written to RAM

as words. To reorder, swap bytes 0 and 3 and bytes 1 and 2 of the 4-byte word

(see SLAVE\_XFER macro):

```

#if defined (SLAVE_SWAP_BYTES)

u_int32_t *swapp;

swapp = (u_int32_t *) startP;

for ( i = 0 ; i < (long)(firmSize/sizeof(u_int32_t)

+ 1); i++ ) {

/* SLAVE_XFER is defined in driver/

fore_atm_drv.h */

SLAVE_XFER(*swapp, *swapp);

swapp++;

}

#endif</pre>

```

The last thing to do is to start the firmware's execution. You can do this by issuing characters into the monitor's address location:

```

static u_int8_t *Hexchs = 0123456789ABCDEF";

Send the firmware the start command ("go

<addr>") */

put_char ('\r');

put_char ('g');

put char ('o');

put char (' ');

entryAddr = firmHeader.entryAddr;

entryAddr <== 16; /* only lower 2-bytes are signifi-</pre>

cant */

for (i = 4; i > 0; i--) {

put char ( Hexchs[ (entryAddr & 0xf0000000) >>

28 ] );

get char();

entryAddr <<= 4;

put char ('\r');

```

At this point, wait for a period (check every 10 milliseconds for 5000 milliseconds, or something more to your liking) for the monitor.bstat flag to be set to 'cp\_running'. Fail if this takes too long.

#### **4.1.2** Notes on the Firmware

Header files included as part of this package define structures used to interface to the firmware. Therefore the structures defined in these headers must match those used

internally by the firmware. The developer should use the firmware images included as part of this package to ensure that these structures match.

Some manuals that may be of interest to developers are "I960 Processor Software Utilities User's Guide" and "Using the GNU/960 Tools" available from Intel.

## 4.1.3 The Host/CP Endian Description

This description presupposes a host processor and associated memory and an cell processor with a local memory region. The host processor can access the cell processor local memory via a bus interface, and the cell processor can access the host memory also by a bus interface. All transfers on the bus occur as 32-bit (4-byte) words. These transfers both begin and end on physical word boundaries in both the host and cell processor memories. The host processor memory may be either little or big endian byte order. (The cell processor memory regions are little endian byte order.) The cell processor sends cells to and receives cells from the network interface as a series of words.

The network interface transmits the bytes from each word to the physical layer and receives the bytes into each word from the physical layer beginning with the most significant byte and ending with the least significant byte. The bytes in an ATM cell payload follow the order that those same bytes were in the original PDU buffer (which is in the host processor memory).

If the host processor memory is defined as little endian byte order, the bus interface must convert the bytes in words that are transferred between the host processor memory and the cell processor. An example of a PDU transmission from a little endian byte order memory will demonstrate why this is necessary. Suppose a host processor with little endian byte order memory. We would like to transmit a twelve-byte buffer containing the string "Hello World!" that begins at a physical memory word with address B.

Buffer in host processor memory:

```

B+00: 'H' B+04: 'o' B+08: 'r' B+01: 'e' B+05: ' ' B+09: 'l' B+02: 'l' B+06: 'W' B+10: 'd' B+03: 'l' B+07: 'o' B+11: '!'

```

The cell processor will transfer this buffer to the network interface. Since the bus only permits word transfers between the host processor memory and the cell processor must read three words.

Words read by the cell processor from the host processor memory (little endian byte ordering):

|      | I  | Most |         |                   | Le  | east |  |  |  |  |  |

|------|----|------|---------|-------------------|-----|------|--|--|--|--|--|

|      |    |      | signifi | significant bytes |     |      |  |  |  |  |  |

| Word | 0: | '1'  | '1'     | 'e'               | 'H' |      |  |  |  |  |  |

| Word | 1: | 'o'  | \ W'    | ' '               | '0' |      |  |  |  |  |  |

| Word | 2: | '!'  | 'd'     | '1'               | 'r' |      |  |  |  |  |  |